除了不确定性,架构的创新也要求芯片从设计到生产应有的周期大幅缩短,否则难以快速满足需求的变化。

早在2018年,美国国防部高级研究计划局(DARPA)就提出了两个新的项目IDEA(Intelligent Design of Electronic Assets)和POSH(Posh Open Source Hardware),目标正是从IP和EDA两个维度缩短芯片设计的流程,节省研发时间。

AI与EDA的融合,能够从根本上解决这些挑战。

AI技术将颠覆芯片设计

今年六月,谷歌团队在国际顶级期刊Nature上发表了一篇题为《一种用于加速芯片设计的布局规划方法(Chip Design with Deep Reinforcement Learning)》的论文,文章指出,利用深度学习,人类工程师需要数月完成的工作,谷歌用AI仅需要6小时就能达到相同效果,提升达到数百倍。

王秉达说:“采用具有AI技术的EDA工具来设计芯片,时间肯定会缩短,这是毋庸置疑的,只是时间缩短的幅度有所不同。”

AI能够缩短芯片设计周期的原因并不复杂,主要是让AI先通过学习,有了知识的累积,在后续使用的过程中遇到相同或者类似的问题能够以更快的速度解决问题,所以带有AI的EDA可以节省芯片设计周期几乎是一个定论。

AI应用于EDA有两种形式,由于芯片设计是一个很长的复杂流程,整个过程中可能需要十几个EDA工具,因此AI既可以应用于EDA点工具中来优化单个芯片设计环节,也可以用于整个芯片设计流程的优化。

如果是用于单个EDA点工具中,其发挥的作用就相当于经验共享,能够让一个只有几年工作经验的工程师,能够达到有丰富经验设计者的水平。“目前芯片架构的设计依赖架构师的经验,如果能够把架构师累积的经验,借助AI技术融入EDA工具中,就可以大幅降低芯片设计的门槛,效率也能大幅提升。”王秉达指出。

如果是贯穿在整个芯片设计流程中的AI,就需要开发者对于AI运行的方式有所了解。王秉达解释,“用AI技术优化芯片设计的流程,需要客户根据实际进度不断进行调节。比如传统的流程中每一步的用时和顺序都很固定,完成前面的步骤才会进入后续步骤。加入AI之后,可能步骤一的时间只需要原来的一半,步骤二时间只需要原来的十分之一,这时候就需要用户进行相应的调整。”

当然,将AI与EDA工具融合不仅可以显著节省研发时间,还能带来芯片性能的提升和设计成本的降低。

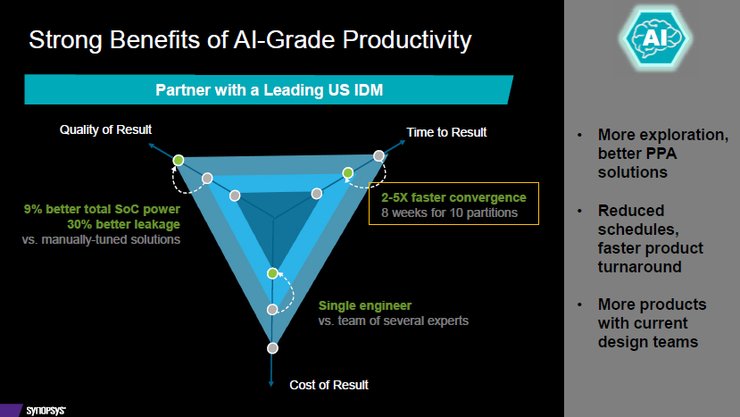

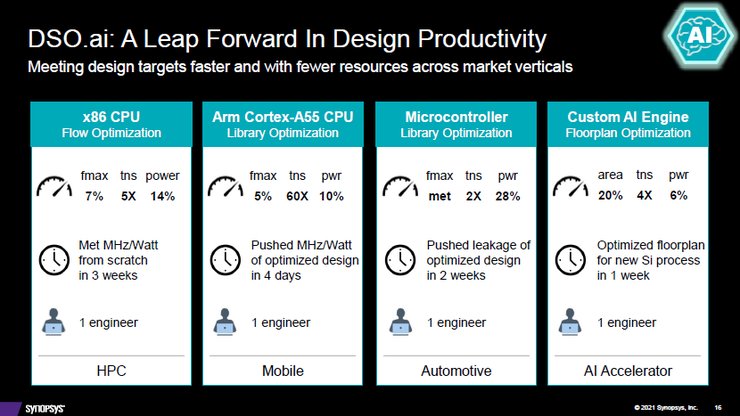

以新思科技的DSO.ai为例,美国头部IDM厂商采用DSO.ai后成果显著,芯片设计的时间提升2-5倍,SoC芯片能耗整体提升9%。将DSO.ai应用于不同类型芯片的设计流程,仅需一位工程师就能带来显著的时间节省和性能提升。

文章插图

文章插图

“不同类型和场景的芯片,AI能带来的提升并不相同。这是因为,芯片整个设计过程需要经历几百万或者上千万个步骤,不同的流程AI带来的提升程度并不一致,同时,上一步优化的结果影响着下一步AI提升的效果。”王秉达指出,“EDA加入AI之后,在节省芯片设计时间的同时,在相同时间内就可以让设计师专注于优化性能和做核心功能的创新,自然更容易设计出性能更好的芯片,整体的成本也能够相应降低。”

未来,从芯片的架构设计、制造以及封装的全流程都会融入AI技术。至于芯片设计的周期能否从以年为单位变为以月为单位,王秉达认为,通过AI + EDA大幅缩短芯片设计环节的周期是明确的,但缩短芯片从设计到制造的整个生命周期还需要整个产业链的共同努力。

芯片差异化竞争的时代

- 设计师|UI设计岗位薪资怎么样

- 芯片|上市仅4个月,跌价1000元,微云台主摄+6nm芯片+4400mAh

- iPhone|iphone14价格被曝!“胶囊”挖孔屏+三星4nm芯片,售价或5999起

- iPhone 14 Pro|iPhone14Pro概念设计:苹果要是能做出来,花一万块钱都要买

- 信息科学技术学院|瞧不起中国芯?芯片女神出手,30岁斩获国际大奖,让美国哑口无言

- 400亿芯片交易接近尾声,英伟达、ARM表明态度,禁止收购后

- 芯片|据称索尼和台积电计划在日本投资70亿美元建芯片工厂

- 体验首款Linux消费级平板,原来芯片和系统全是国产

- 算力|不靠显卡!NVIDIA在中国焕发第二春:自动驾驶芯片被车厂爆买

- excel|苹果换设计师了?iPhone14“定妆照”曝光,库克的审美终于提高了