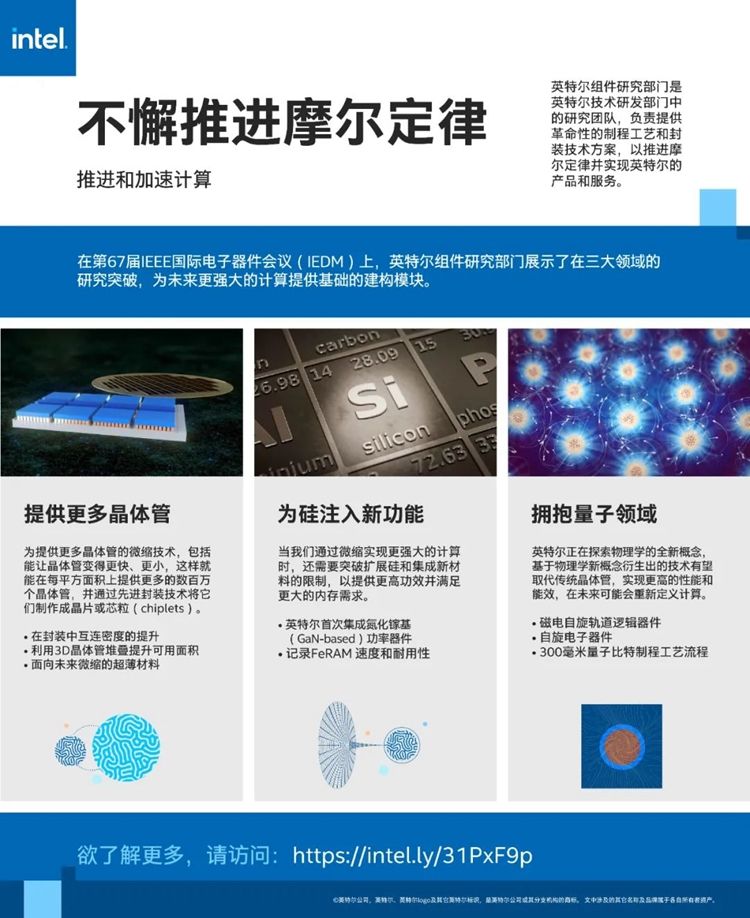

对于整个半导体行业来说,摩尔定律指导着半导体领域不断发展,特别是对于CPU这样的复杂设备来说,晶体管密度与数量将会决定CPU的性能,然而近年来由于工艺和技术的限制,晶体管密度在一定程度上属于原地踏步的状态,从而导致CPU性能并没有一个突飞猛进的变化,或者说在功耗以及发热上无法取得一个平衡。不过作为半导体领域的大哥,英特尔在国际电子器件会议上公布了他们对于半导体工艺制程的最新研究成果,根据相关的成果,未来英特尔的芯片晶体管密度将会得到极大的提升。

文章插图

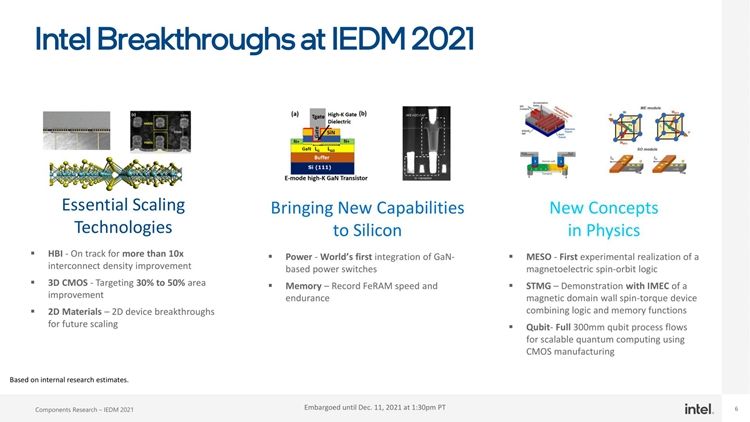

首先是晶体管的密度,这个指标将会决定在一定面积内的晶体管数量,对此英特尔称未来将会采用全新的晶体管微缩技术,让晶体管变得更小,更快,相比较于现在的晶体管密度,未来通过全新技术,可以在每平方面积上提供更多的数以百万级的晶体管。同时也将增加芯片封装中的互连密度,最多提升幅度达到10倍。同时借助3D晶体管堆叠技术可以实现芯片的可用面积,让芯片内塞入更多的晶体管。同时英特尔也希望借助全新的微缩材料,让晶体管的体积降低50%,而性能没有太大的变化。

文章插图

【 制造|Intel公布全新晶体管制造技术:体积缩小50%,封装密度提升10倍】除此之外,英特尔也将在芯片中集成氮化镓基功率器件,实现更加强大的计算能力。而在量子领域,英特尔也将表示未来将会推出基于量子技术的终端产品以取代目前的晶体管,从而实现计算力的大幅提升,甚至在一定程度上重新定义未来的计算,可以说英特尔认为对于未来的半导体行业来说,量子计算的引入将会彻底改变整个计算市场。当然这些技术从推出到落地还有数年的时间,消费者还是看看就行了、

- CPU|元宇宙+高端制造+人工智能!公司已投高科技超100亿,股价仅3元

- 智能制造|企业转型的新时代,夹缝中求生存

- Linux|电脑城卖的CPU是intel而不是AMD,和实体店不喜欢卖小米手机是一个道理

- 阿里巴巴|被苹果无辜“踢出局”,引发央视点名,国产制造该何去何从?

- 1月14日|奇瑞瑞虎8plus插电混动车型公布售价15.18万和16.5

- Intel找台积电打造专属3nm的工厂:并非短期合作?

- 工厂|为Intel单独建3nm工厂?台积电回应合作问题:不过度依赖单一客户

- intel公司|苹果芯片总监刚被Intel挖走,技术大咖又跳槽微软

- 芯片|又一巨头或对英特尔“下手”,美方希望重掌芯片制造,机会渺茫!

- 大众网·海报新闻记者 单姗 单文玲 潍坊报道为助力企业健康快速成长|“小巨人”华特磁电“磁”实发展 跑出潍坊制造业加速度