文章图片

文章图片

文章图片

文章图片

该来的终究会来 , 台积电担心的事还是发生了 。

台积电第一 , 三星第二 , 这是过去对半导体市场的普遍评价 。 然而 , 随着全球首个3nm即将量产 , 台积电过去的优势将被打破 。

台积电没想到 , 首个量产的3nm芯片 , 竟然会出自别家之手 , 而且该芯片还采用了全新的3GAE 工艺技术 , 全球半导体发展也可能因此迎来分水岭 。

三星近日宣布 , 有望在未来几周内 , 实现3nm芯片的量产 。 不仅如此 , 三星也将成为全球首个 , 利用环栅场效应晶体管 , 实现高制程芯片量产的企业 。

让台积电更加揪心的是 , 自己生产的4nm天玑9000芯片 , 近日又被爆出功耗高和发热问题 。

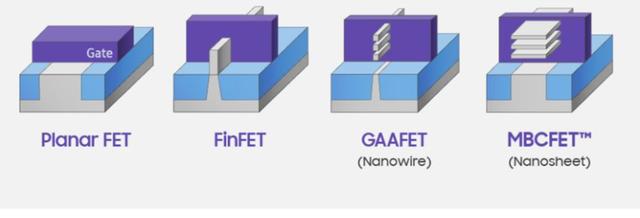

台积电采用的是FinFET结构 , 这种结构在应对高制程工艺的芯片时 , 本身就有很多问题 。

例如前面提到的功耗和发热问题 , 就是因为FinFET结构的晶体管 , 随着芯片尺寸的缩小 , 芯片内部的沟道长度变窄 , 使得栅极对沟道的控制能力变差 , 出现的漏电现象导致的 。

然而 , 三星采用的GAA 晶体管结构 , 在这方面 , 却有着天生的优势 。

在GAA晶体管中 , 沟道呈现为水平状 , 而且会被栅极包围 。 再加上GAA的沟道 , 是利用外延和选择性材料去除形成的 , 研发人员可以通过调整通道的宽度 , 来精确的控制沟道的状态 。

一般情况下 , 沟道越宽 , 对性能的提升就越明显 , 而沟道越窄 , 则更有助于降低功耗 。 这意味着 , 研发人员可以根据实际需要 , 更加灵活地控制沟道的宽度 , 并在功耗和性能之间 , 找到更优的平衡点 。

GAA晶体管是一种全新的结构 , 能从芯片设计的底层 , 改变过去工艺可能出现的漏电现象 , 对提高芯片性能 , 和降低功耗有着双重叠加优势 。

有业内人士认为 , GAA结构的晶体管 , 有望使得芯片的尺寸 , 在原有的基础上 , 再降低25%左右 , 实现新的突破 。

反观台积电 , 依旧徘徊在FinFET结构的痛点上 , 不能自拔 。 为了应对FinFET结构上劣势 , 台积电只能退而求其次 , 通过5纳米加强版N4P的3纳米 , 来为苹果供应下一代处理器 。

台积电原以为 , 自己的芯片份额无人能敌 , 高制程工艺技术所向披靡;殊不知 , 全球半导体产业 , 已经悄然迎来一场变局 。

除了三星的GAA新工艺技术 , 英特尔也开始在半导体技术研究上发力 , 有消息称 , 英特尔计划在2024年之前 , 接管全球半导体制程的领导地位 。

不仅如此 , 英特尔还获得了阿斯麦下一代光刻机的优先供货权 , 这让英特尔如虎添翼 。

根据阿斯麦的规划 , 新一代的EUV光刻机将采用高数值孔径 , NA值将由过去的0.33 , 提升至0.55 。

NA值是评估光刻机先进程度的重要参数 , NA值越高 , 意味着在同等大小的晶圆上 , 能刻蚀的电路图分辨率会更高 , 芯片所包含的晶体管数量也会更多 。

由于台积电在芯片供货方式上 , 采取了区别对待 , 让各地区如坐针毯 , 包括欧美、日韩等地区 , 均已启动了新的半导体发展计划 。

- 大众电动车的中国战役怎么打?从软件“本土化”开始

- 酷睿处理器|发力大电池,6100mAh国产新机试产,12+256G定在1399元

- 零售业|马云或许没有吹牛,电商或将被淘汰,全新商业模式已经悄然而生

- vivo x80|vivo X80系列雅致设计,双电芯闪充很给力

- 5G|5G新通话“新”江湖电信联通联手的5G超清视话胜算几何

- 电池|内卷狂潮!4月值得关注的5款新机,五一购机优选

- 风扇|中国牛人发明“神奇风扇”,83小时一度电,风感不输4999元戴森!

- 核电站|红沿河核电站6号机组首次并网发电

- 投影仪|手机耗电太快怎么解决?

- 有望取代电三轮 五菱E10交付顺丰:快递小哥排队体验