器件|解读英特尔芯片制造技术突破:互连密度增10倍以上,新工艺将逻辑微缩提升超30%

文章插图

芯东西(公众号:aichip001)

作者 | 高歌

编辑 | Panken

芯东西12月14日报道,今天,英特尔制造、供应链和营运集团副总裁兼战略规划部联席总经理卢东晖向芯东西等媒体详细解读了英特尔在今年IEEE国际电子器件会议(IEDM)上发布的8篇论文。

这是英特尔首次在这一学术会议上发布如此数量的论文,据卢东晖分享,本次英特尔发布的很多新研究特点是基于当前的芯片制造工艺,之后有应用于现有的产线的可能,对英特尔IDM 2.0战略有着重要意义。

本次在IEDM会议上发表论文的是英特尔组件研究部门,这是英特尔专注于前沿研发的部门,被称作“英特尔技术研发部门中的研究团队”,其发表的论文主要集中在晶体管微缩技术、在功率器件和内存方面基于新材料的研究和量子计算器件3个领域。

文章插图

英特尔在IEDM 2021上的研究突破

一、新互连技术提升10倍密度,3D CMOS堆叠降低50%芯片面积对于先进制程的演进,卢东晖将其比作爬山,人们知道山顶在哪里,但是不清楚路在哪里,也不确定自己到底能否登顶、会花费多少时间,这都是行业领先者需要考虑的问题。

摩尔定律成为了推动行业不断投入研发的重要原因,而且这一定律对产业界合作也起到了关键作用。此前,芯片制造、材料、设备厂商产品迭代时间并不一致,产品迭代较为混乱,整个产业链合作效率较低。

摩尔定律则在一定程度上成为了芯片产业链的路线图,上下游厂商可以在相近的时间节点进行产品迭代,使行业合作效率更高。

同时,更高的组件密度能够让芯片实现更高的吞吐量、增加新的特性和功能、降低成本、提高能效等。卢东晖以3D NAND闪存为例强调了芯片制程代差对于企业的重要,他提到领先两代的产品以30%的良率进行生产,其成本就要低于90%良率生产的落后产品,更高的制程代差甚至出现“在月球造都要更便宜”的现象。

具体到本次发布的论文,英特尔在晶体管微缩领域的研究突破主要为封装中互连密度的提升、3D堆叠的CMOS晶体管结构和新的2D材料。

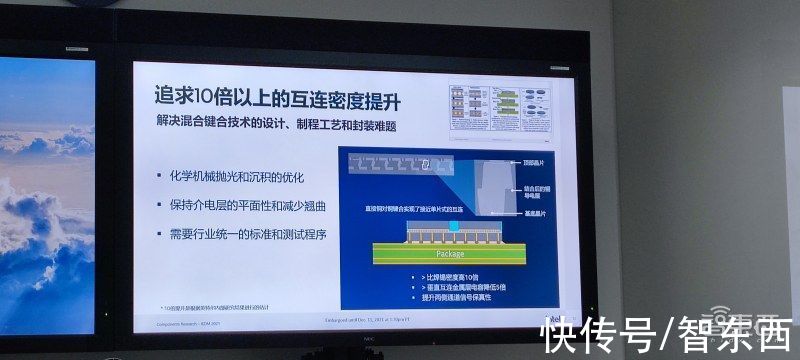

在封装互连密度的研究中,英特尔研究团队实现了铜对铜的近单片式互连。新的互连方式比焊锡密度高10倍,使垂直互连金属层电容低5倍。

不过这对表面平整度要求更高,需要厂商对化学机械抛光和沉积工序进行优化,保持介电层的平面行和减少翘曲,并要有行业统一的标准和测试程序作为支撑。

文章插图

新互连技术展示

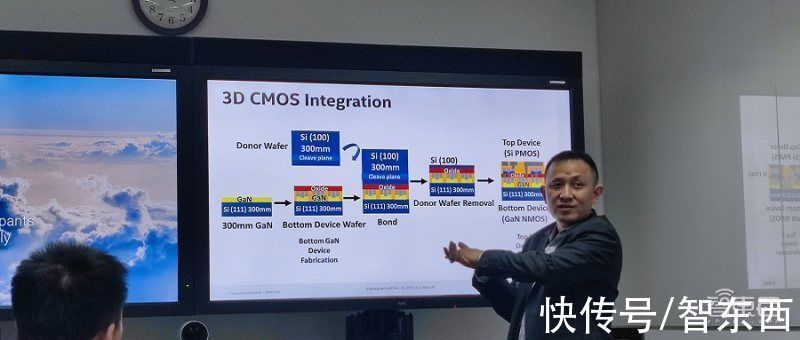

在晶体管结构上,英特尔实现了3D CMOS的堆叠,通过将源极和漏极直接堆叠的方式,降低了30%-50%的芯片面积。

卢东晖称,这有两种不同的实现方式,一种是依序,即上下层晶圆依序堆叠加工;另一种则是自对准,即上下层晶圆对准后同时进行架构,能够将栅极间距缩减至55nm。

在卢东晖个人看来,3D CMOS堆叠结构可能会在GAA(全环绕栅极)之后被用于先进制程芯片生产。

文章插图

3D CMOS堆叠技术展示

在新材料方面,英特尔发现了一种TMD(过渡金属硫化物),这是一种2D材料,其单层结构仅有数个原子厚度,能够克服硅半导体在缩减到一定规模后出现的量子隧穿问题。

在论文中,英特尔使用锑(Sb)和钌(Ru)两种金属作为NMOS两级,使其间距从15nm缩减至5nm。卢东晖称,这种新材料可用于硅基材上,构建新的芯片结构,实现高性能异构。

- 打脸!华为在美国,用专利把英特尔、苹果、微软、高通打败了

- 沉浸式|海外观察丨未来 10 大科技趋势预测全解读(上)

- 三星|这一招漂亮!英特尔对华“宣战”48小时内,中方果断亮出一张王牌

- 芯片|又一巨头或对英特尔“下手”,美方希望重掌芯片制造,机会渺茫!

- javascript|帕特·基辛格被任命为英特尔CEO已有一年

- 英特尔|Intel未发布下代至强被开盖:完整64个核心、只开启56个

- 中小企业|海纳百川,顺势而为!鹏博士副总裁李炜解读云计算战略2.0

- playstation5|基本的元器件检测 常用方法汇总

- 台积电|台积电解读财报:21年营收568.2亿美元创新高 北美才是最大市场

- 英特尔|朝7家企业“下手”,英特尔启动新计划!原来中芯只是一个开始?