mb|IBM,预言了缓存的未来?

文章插图

文 | 内容由半导体行业观察,编译自「anandtech」

在上周的 Hot Chips 大会上,IBM 宣布了其新的大型机 Z 处理器。这是一个很有趣的设计,值得大肆讨论一番。但在本文里,我想特别关注该核心设计的一个功能。

IBM Z 处理器以拥有大型 L3 缓存而闻名,并以单独的全局 L4 缓存芯片作为后盾,该芯片可作为多个处理器插槽之间的缓存——IBM 已经通过新的 Telum 芯片取消了这一点——没有 L4,但有趣的是,没有L3。

他们所做的可能预示着片上缓存设计的未来。

文章插图

缓存的简要入门任何现代处理器都有与其关联的多级缓存。它们由容量、延迟和功耗分开——最靠近执行端口的最快缓存往往很小,然后我们有更大的缓存,速度稍慢,然后可能是在我们到达主内存之前的另一个缓存。缓存的存在是因为 CPU 内核现在想要数据,如果它全部保存在 DRAM 中,那么它每次获取数据将需要 300 多个周期。

【 mb|IBM,预言了缓存的未来?】现代 CPU 内核会提前预测它需要什么数据,然后先将它从 DRAM 带入其缓存,这样的话内核可以在需要时更快地获取它。一旦缓存线被使用,它通常会从最近的一级缓存 (L1) 被“赶”到下一级缓存 (L2),或者如果 L2 缓存已满,则 L2 中最旧的缓存线将被驱逐到一个L3 缓存以腾出空间。这意味着如果再次需要该数据线,它不会离开内核太远。

文章插图

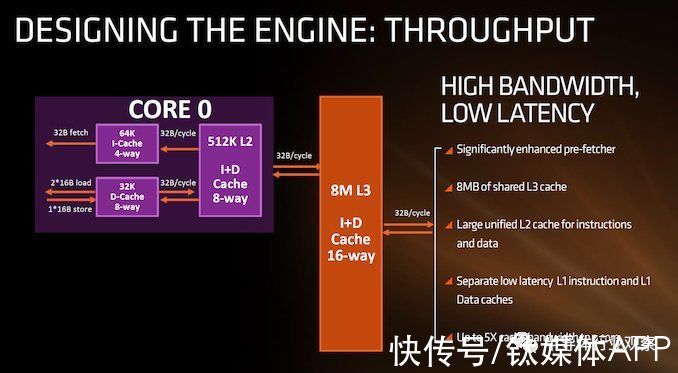

AMD 第一代 Zen 处理器上的 L1、L2 和共享 L3 的展示

还有私有和共享缓存。

现代处理器设计具有多个内核,在这些内核中将至少有一个只有该内核才能访问的私有缓存(L1)。在此之上,缓存可以是仍位于核心本地的私有缓存,也可以是任何核心都可以使用的共享缓存。

例如,英特尔 Coffee Lake 处理器有八个内核,每个内核都有一个 256 KB 的私有 L2 缓存,但在芯片范围内,所有八个内核之间有一个 16 MB 的共享 L3。这意味着,如果单个内核想要,它可以不断地将数据从较小的 L2 赶到较大的 L3 中,并且如果要重用该数据,则可以拥有一个资源池。不仅如此,如果第二个内核也需要一些数据,他们可以在共享的 L3 缓存中找到它,而不必将其写出到主内存并在那里获取。使事情复杂化。最终的结果是缓存有助于减少执行时间,并在需要或需要时从主内存中引入更多数据。

权衡考虑到这一点,您可能会问为什么我们在处理器上看不到 1 GB 的 L1 或 L2 缓存。这是一个完全有效的问题。这里有许多因素在起作用,包括芯片面积、效用和延迟。

芯片面积很容易首先解决——因为最终每个缓存结构可能只有一个定义的空间。当你在硅中设计内核时,可能有一种最好的方法来布置内核的组件以获得最快的关键路径。但是缓存,尤其是L1缓存,必须在靠近需要数据的地方。如果您想要一个大的 128 KB L1 缓存,那么设计与具有 4 KB L1 缓存的芯片布局将会大不相同。所以这里有一个权衡。

除了 L1,L2 缓存有时也是芯片面积的大量消耗者,虽然它(通常)不受其他核心设计的限制,但它仍然必须与需要在芯片上。任何大型共享缓存,无论最终成为 2 级缓存还是 3 级缓存,通常都可能是芯片的最大部分,具体则取决于所使用的工艺节点。

实用性也是一个关键因素——我们在 AnandTech 上主要谈论通用处理器,尤其是那些基于 x86 构建的用于 PC 和服务器的处理器,或者用于智能手机和服务器的 Arm,但是有很多专用设计,它们的作用是针对特定的工作量或任务。如果处理器核心需要做的只是处理数据,例如相机 AI 引擎,那么该工作负载就是一个明确定义的问题。这意味着可以对工作负载进行建模,并且可以优化缓存的大小以提供最佳性能/功耗。

- iphone13 pro|粉丝买美版iPhone13Pro,躲过了网络锁,却没想到有配置锁!

- 酷睿处理器|关键数据出炉,京东比阿里差远了

- 魅族|对不起!魅族,这次确实令人失望了

- 华为|问界M5风光无限,赛力斯SF5暗自神伤,华为或许低估了造车这事?

- 央视公开“支持”倪光南?柳传志该醒悟了

- 苹果|最具性价比的苹果手机来了,降价2120元,iPhone12已跌至冰点价

- 为了你的iPhone能磁吸充电,苹果又花了5亿买材料

- 5G|关于5G,华为赢了

- 造车|苹果造车一波三折,缺了一家“富士康”

- 百度|马化腾的一句话,腾讯市值一小时暴涨1400亿港币,马云格局还是小了