|2nm芯片的EDA,实行禁运?联发科、富士康:我们来研发

文章图片

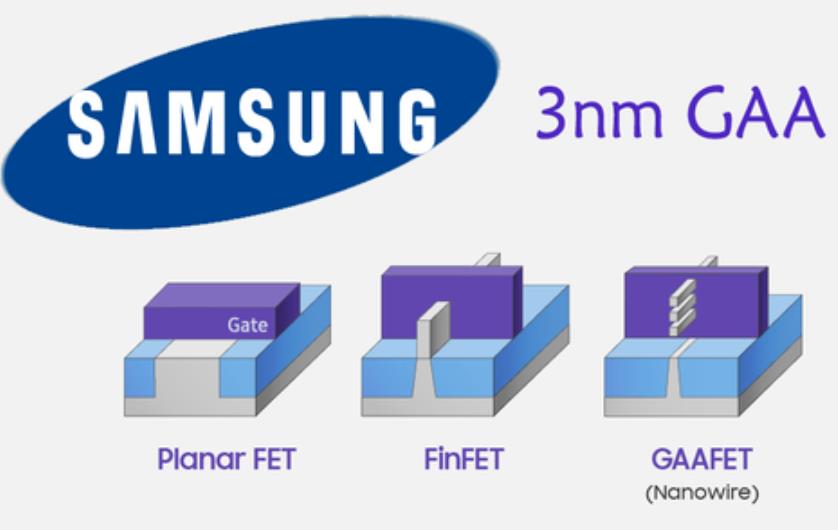

众所周知 , 三星的3nm芯片 , 抛弃了老迈的FinFET晶体管技术 , 采用了最新的GAAFET晶体管技术 。

而台积电在3nm时虽然采用了FinFET技术 , 但2nm时会采用GAAFET晶体管技术 。 还有IBM、intel之前披露的技术来看 , 到2nm时 , 也一定会用上GAAFET技术 。

这意味着 , 只要进入2nm , 就一定会使用GAAFET晶体管技术 。

也正因为如此 , 所以前段时间 , 美国针对中国大陆 , 实行了新一轮的技术管制 , 其中用于设计GAAFET架构的EDA工具 , 就被列入了禁运名单 。

美国的目的很明显 , 就是卡住中国大陆的芯片设计能力 , 让其暂时止步于3nm , 不能进入2nm , 因为目前只有美国的厂商 , 才能推出用于2nm芯片的EDA工具 。

甚至从全球EDA格局来看 , 美国三大巨头Synopsys、Cadence、Siemens EDA(总部在美国) , 占了全球80%的份额 , 另外美国还有ANSYS、Keysight Technologies , 这两大EDA企业 , 排名全球第四、五名 , 也占了8%左右份额 。

所以 , 美国只要卡住EDA , 基本上也就卡住了中国大陆的芯片设计能力 , 毕竟国产EDA工具 , 流程环节支持不全面 , 至少在40%没有涉及到 。 同时工艺大多只能覆盖到14nm 。

不过近日 , 有两家中国厂商 , 打算自己研发2nm的EDA工具软件 , 这两家厂商就是联发科 , 以及富士康 。

联发科表示 , 要与台大电资学院及至达科技合作 , 将 AI 人工智能技术应用于 IC 设计 , 往GAAFET技术前进 。

富士康也表示 , 自己要布局半导体领域 , 锁定先进封装、测试、装备及材料、EDA、IC设计等 , 其中IC设计及EDA领域 , 也要早点实现对GAAFET晶体管技术的支持 。

为何台系厂商要研发EDA , 还要实现对GAAFET晶体管技术的覆盖 , 原因在于台系厂商 , 其实也高度依赖美国的EDA , 所以也想着自给自足 , 不受美国控制 。

【|2nm芯片的EDA,实行禁运?联发科、富士康:我们来研发】不过 , EDA软件 , 不仅仅只是技术问题 , 还是生态问题 , 因为这涉及到IC设计企业 , 晶圆制造企业 , 封测企业之是的协同 , 就看联发科、富士康们如何推进了 。

- 9月8日|价格实惠的大屏幕 iPhone 14 Plus 可能更适合你

- 芯片|中国真有人叫“支付宝”,他曾起诉马云赔偿100万,被如此回应

- Apple Watch|炫富也要真诚,视频炫富涨粉的玩法

- 知乎|罗敏陆正耀,在预制菜的风口惨痛跌倒

- 提起OLED屏笔记本的普及|OLED屏笔记本将日益增加

- 环保笔记本是什么样的产品?其实我们之前介绍过|12代酷睿4299元轻薄本,这一点还是很值得考虑的

- 荣耀70是一款中端机型|荣耀 70 是一款出色的智能手机

- 未来者两款高配台式机的性能还是很足的

- 余承东|苹果iPhone 14带着最惊艳的体验来了,5999元起售!还有最硬核手表

- 苹果|苹果14/14 Plus正式发布:还是熟悉的配方,799刀起