文章图片

【物联网|据报道,台积电第一阶段 3nm 生产的良率高达 80%】

本周 , 台积电已经正式开始使用其 N3 制程工艺量产其 3nm 芯片 , 与 N5 技术相比 , N3 技术将提供高达 70% 的逻辑密度增益 , 在相同功率下速度提升高达 15% , 在相同速度下功率降低高达 30% , 相比于 N4 工艺的 4nm 的芯片 , 综合性能提升大约在20%~25%左右 。

根据 Business Next 近日给出的分析数据显示 , 台积电的 N3 收益率可能在 60%-70% 范围内 , 或高达 75% 至 80% 。关键是对于第一批 N3 工艺的晶圆来说 , 这个表现已经相当不错了 。 另一位分析师 Dan Nystedt 表示 , 台积电第一阶段的 N3 工艺的良率与之前第一阶段 N5 工艺的良品率相似 , 并且随着技术成熟 , 未来良品率会达到 80%甚至更高 。

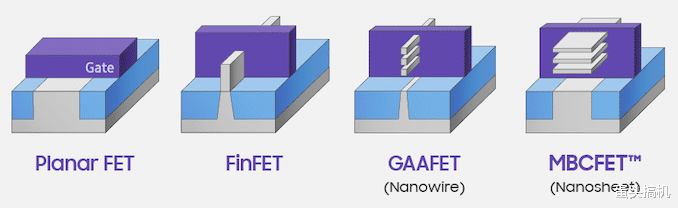

相比之下 , 台积电的竞争对手三星表现并不乐观 , 根据调查数据显示 , 三星代工的 3GAE 工艺的第一阶段良品率在10%到20%之间 , 相差巨大 。 其主要原因是三星的 3nm 环栅 (GAA) 晶体管工艺与台积电的 FinFET 工艺在结构上存在重大差异 , 三星本身采用的环栅 (GAA) 晶体管 , 可以更好地控制晶体管的电流 。这是因为 GAA 晶体管具有垂直堆叠的纳米片以覆盖通道的所有四个侧面 , 电源效率和运算能力理论应该更高 。 但目前三星3nm 的GAA工艺存在一定缺陷 , 导致成品率并未达到预期 。

台积电表示 , 未来技术成熟后 , 会在 2nm 芯片阶段改用 GAA 工艺, 确保其良品率在可控范围内 。

- 1998年一位老人去世,我们欠他一句感谢,物理界欠他一个诺贝尔奖

- 大数据|一冷门国企工资单曝光,每天工作2小时,待遇可媲美互联网大厂

- 张勇|马化腾、刘强东、张勇相继发飙,互联网大厂的日子也不好过?

- 新年礼物怎么选?感恩回馈季华为智慧屏了解一下!

- 万物云: “创新先锋”是如何炼成的

- 京东物流|CES2023将至 你的下一台游戏本或许只需要4000元

- 电子商务|互联网消费被吐槽?但没了外卖和电商,就真的能推动实体经济吗?

- MongoDB|选新年礼物来华为感恩回馈季,多个鸿蒙套装值得入手!

- 裁员|华为、小米等互联网公司年终岁尾忙裁员,体制内工作才是真的香

- 亚马逊|华为、小米等互联网公司年终岁尾忙裁员,体制内工作才是真的香